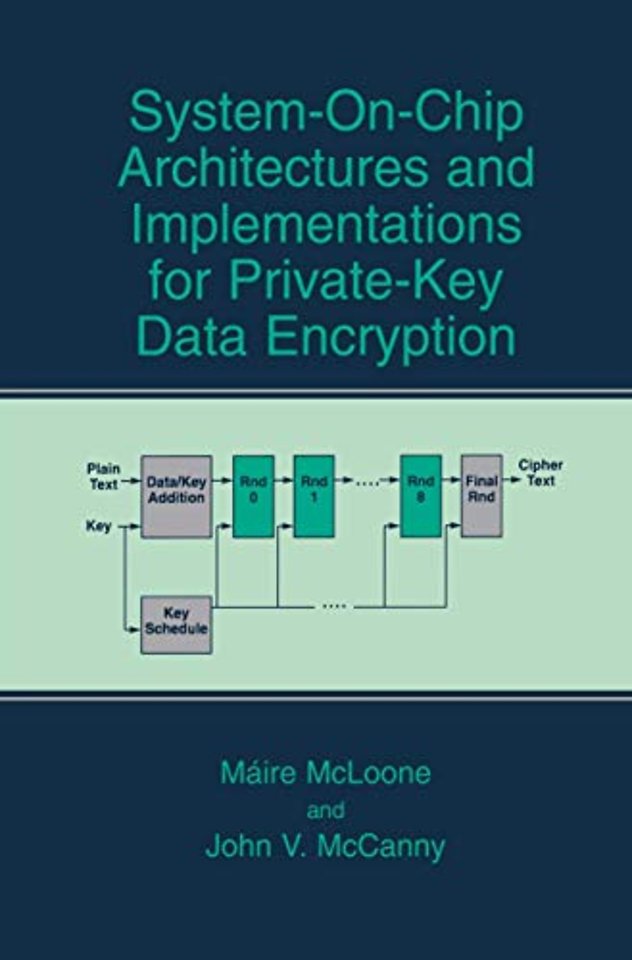

System-on-Chip Architectures and Implementations for Private-Key Data Encryption

Gebonden Engels 2003 2003e druk 9780306478826Samenvatting

In System-on-Chip Architectures and Implementations for Private-Key Data Encryption, new generic silicon architectures for the DES and Rijndael symmetric key encryption algorithms are presented. The generic architectures can be utilised to rapidly and effortlessly generate system-on-chip cores, which support numerous application requirements, most importantly, different modes of operation and encryption and decryption capabilities. In addition, efficient silicon SHA-1, SHA-2 and HMAC hash algorithm architectures are described. A single-chip Internet Protocol Security (IPSec) architecture is also presented that comprises a generic Rijndael design and a highly efficient HMAC-SHA-1 implementation.

In the opinion of the authors, highly efficient hardware implementations of cryptographic algorithms are provided in this book. However, these are not hard-fast solutions. The aim of the book is to provide an excellent guide to the design and development process involved in the translation from encryption algorithm to silicon chip implementation.

Specificaties

Lezersrecensies

Inhoudsopgave

Rubrieken

- advisering

- algemeen management

- coaching en trainen

- communicatie en media

- economie

- financieel management

- inkoop en logistiek

- internet en social media

- it-management / ict

- juridisch

- leiderschap

- marketing

- mens en maatschappij

- non-profit

- ondernemen

- organisatiekunde

- personal finance

- personeelsmanagement

- persoonlijke effectiviteit

- projectmanagement

- psychologie

- reclame en verkoop

- strategisch management

- verandermanagement

- werk en loopbaan